- 您现在的位置:买卖IC网 > Sheet目录324 > EVAL-ADUC7060QSPZ (Analog Devices Inc)KIT DEV QUICK START ADUC7060

�� �

�

�

�ADuC7060�

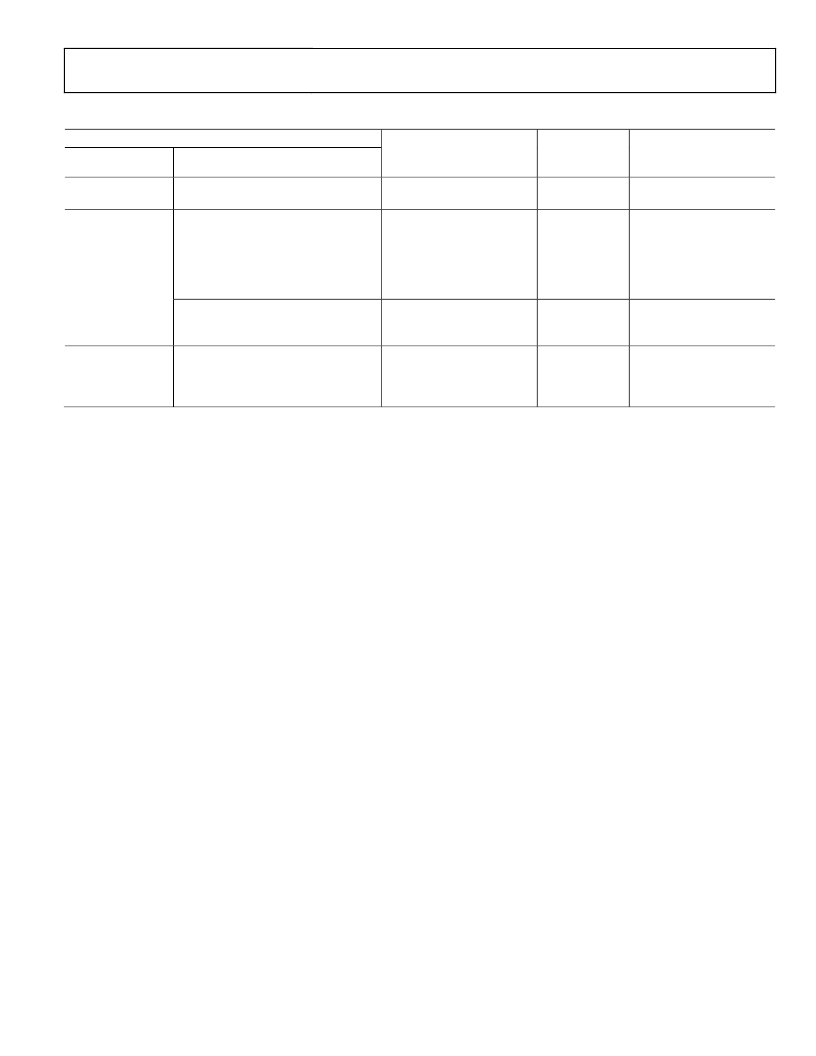

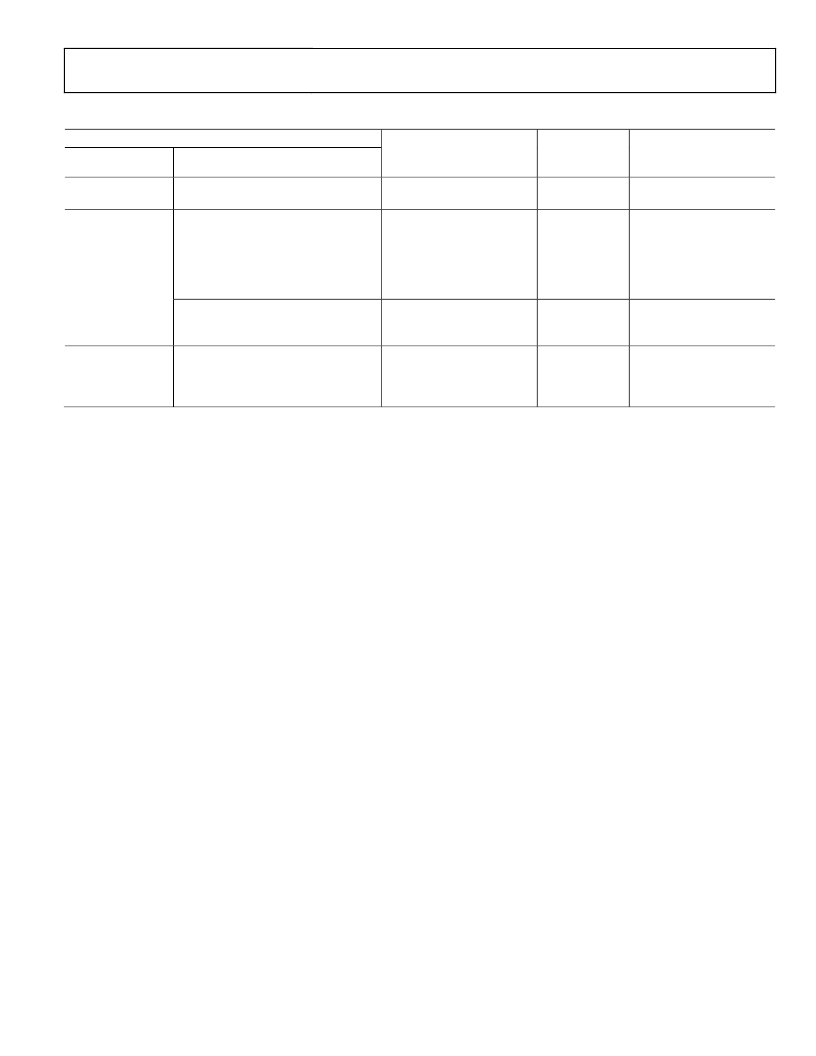

�Table� 37.� Example� Scenarios� for� Using� Diagnostic� Current� Sources�

�Diagnostic� Test�

�Detected�

�Measurement�

�Register� Setting�

�ADC0DIAG[1:0]� =� 0�

�ADC0DIAG[1:0]� =� 1�

�Description�

�Convert� ADC0/ADC1� as� normal� with�

�diagnostic� currents� disabled.�

�Enable� a� 50� μA� diagnostic� current�

�source� on� ADC0� by� setting�

�ADC0DIAG[1:0]� =� 1.� Convert� ADC0� and�

�ADC1.�

�Normal� Result�

�Expected� differential� result�

�across� ADC0/ADC1.�

�Main� ADC� changes� by�

�ΔV� =� +50� μA� ×� R1.� For�

�example,� ~100� mV� for� R1� =�

�2� kΩ.�

�Fault� Result�

�Short� circuit.�

�Short� circuit�

�between� ADC0�

�and� ADC1.�

�Short� circuit�

�for� Fault�

�Primary� ADC� reading� ≈� 0� V�

�regardless� of� PGA� setting.�

�Primary� ADC� reading� ≈� 0� V�

�regardless� of� PGA� setting.�

�between� R1_a�

�and� R1_b.�

�Convert� ADC0� in� single-ended� mode�

�with� diagnostic� currents� disabled.�

�Expected� voltage� on� ADC0.�

�ADC0� open�

�circuit� or� R1�

�open� circuit.�

�Primary� ADC� reading� =�

�+full� scale,� even� on� the�

�lowest� PGA� setting.�

�ADC0DIAG[1:0]� =� 3�

�Enable� a� 50� μA� diagnostic� current�

�source� on� both� ADC0� and� ADC1� by�

�Primary� ADC� changes� by� ΔV�

�=� 50� μA� ×� (R1� ?� R2);� that� is,�

�R1� does� not�

�match� R2.�

�Primary� ADC� reading� >�

�10� mV.�

�setting� ADC0DIAG[1:0]� =� 3.� Convert�

�ADC0� and� ADC1.�

�~10� mV� for� 10%� tolerance.�

�Sinc3� Filter�

�The� number� entered� into� Bits[6:0]� of� the� ADCFLT� register� sets�

��for� further� details� on� the� decimation� factor� values.�

�The� range� of� operation� of� the� sinc3� filter� (SF)� word� depends� on�

�whether� the� chop� function� is� enabled.� With� chopping� disabled,�

�the� minimum� SF� word� allowed� is� 3� and� the� maximum� is� 127,�

�giving� an� ADC� throughput� range� of� 50� Hz� to� 2� kHz.�

�For� details� on� how� to� calculate� the� ADC� sampling� frequency�

�based� on� the� value� programmed� to� the� SF[6:0]� in� the� ADCFLT�

�register,� refer� to� Table� 44� for� more� details.�

�ADC� CHOPPING�

�The� ADCs� on� the� ADuC7060� implement� a� chopping� scheme�

�whereby� the� ADC� repeatedly� reverses� its� inputs.� Therefore,� the�

�decimated� digital� output� values� from� the� sinc3� filter� have� a�

�positive� and� negative� offset� term� associated� with� them.� This�

�results� in� the� ADC� including� a� final� summing� stage� that� sums�

�and� averages� each� value� from� the� filter� with� previous� filter�

�output� values.� This� new� value� is� then� sent� to� the� ADC� data�

�MMR.� This� chopping� scheme� results� in� excellent� dc� offset� and�

�offset� drift� specifications� and� is� extremely� beneficial� in�

�applications� where� drift� and� noise� rejection� are� required.�

�Programmable� Gain� Amplifier�

�The� primary� ADC� incorporates� an� on-chip� programmable� gain�

�AVDD.� They� are� individually� configurable� to� give� a� current�

�range� of� 200� μA� to� 1� mA.� The� current� step� sizes� are� 200� μA.�

�These� current� sources� can� be� used� to� excite� an� external� resistive�

�bridge� or� RTD� sensors.� The� IEXCON� MMR� controls� the�

�excitation� current� sources.� Bit� 6� of� IEXCON� must� be� set� to�

�enable� Excitation� Current� Source� 0.� Similarly,� Bit� 7� must� be� set�

�to� enable� Excitation� Current� Source� 1.� The� output� current� of�

�each� current� source� is� controlled� by� the� IOUT[3:0]� bits� of� this�

�register.�

�It� is� also� possible� to� configure� the� excitation� current� sources� to�

�output� current� to� a� single� output� pin,� either� IEXC0� or� IEXC1,�

�by� using� the� IEXC0_DIR� and� IEXC1_DIR� bits� of� IEXCON.� This�

�allows� up� to� 2� mA� to� output� current� on� a� single� excitation� pin.�

�ADC� Low� Power� Mode�

�The� ADuC7060� allows� the� primary� and� auxiliary� ADCs� to� be�

�placed� in� low� power� operating� mode.� When� configured� for� this�

�mode,� the� ADC� throughput� time� is� reduced,� but� the� power�

�consumption� of� the� primary� ADC� is� reduced� by� a� factor� of�

�about� 4;� the� auxiliary� ADC� power� consumption� is� reduced� by� a�

�factor� of� roughly� 3.� The� maximum� ADC� conversion� rate� in� low�

�power� mode� is� 2� kHz.� The� operating� mode� of� the� ADCs� is�

�controlled� by� the� ADCMDE� register.� This� register� configures�

�the� part� for� either� normal� mode� (default),� low� power� mode,� or�

�low� power� plus� mode.� Low� power� plus� mode� is� the� same� as� low�

�power� mode� except� that� the� PGA� is� disabled.� To� place� the� ADCs�

�in� low� power� mode,� the� following� steps� must� be� completed:�

�amplifier� (PGA).� The� PGA� can� be� programmed� through� 10�

�different� settings� giving� a� range� of� 1� to� 512.� The� gain� is�

�controlled� by� the� ADC0PGA[3:0]� bits� in� the� ADC0CON� MMR.�

�Excitation� Sources�

�The� ADuC7060� contains� two� matched� software� configurable�

�current� sources.� These� excitation� currents� are� sourced� from�

�?�

�?�

�?�

�ADCMDE[4:3]—Setting� these� bits� enables� normal� mode,�

�low� power� mode,� or� low� power� plus� mode.�

�ADCMDE[5]—Setting� this� bit� configures� the� part� for� low�

�power� mode.�

�ADCMDE[7]—Clearing� this� bit� further� reduces� power�

�consumption� by� reducing� the� frequency� of� the� ADC� clock.�

�Rev.� 0� |� Page� 35� of� 100�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EVAL-ADUC845QSPZ

KIT DEV QUICK START ADUC845

EVAL-ADUM3070EBZ

BOARD EVAL FOR ADUM3070

EVAL-SDP-CB1Z

BOARD EVALUATION FOR SDP-CB1

EVB51JM128

BOARD EVAL FOR MCF51JM128 MCU

EVBQE128

BOARD EVAL FLEXIS QE128 FAMILY

F2068

PNL FIBERGLASS 18.44X14.44" WHT

FAN3100CMPX

IC GATE DRVR SGL CMOS 2A 6MLP

FAN3111CSX

IC GATE DVR 1CH 1A LOW SOT23-5

相关代理商/技术参数

EVAL-ADUC7060QSPZU1

制造商:Analog Devices 功能描述:

EVALADUC7060QSPZU2

制造商:Analog Devices 功能描述:QUICK START DEVELOPMENT SYSTEM - Boxed Product (Development Kits)

EVAL-ADUC7061MKZ

功能描述:开发板和工具包 - ARM Quick Start Development System

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

EVAL-ADUC7061MKZ

制造商:Analog Devices 功能描述:ADUC7061MKZ EvaluationBoard

EVAL-ADUC7061MKZU2

制造商:Analog Devices 功能描述:PN may be NE CE 制造商:Analog Devices 功能描述:EVALUATION CONTROL BOARD - Boxed Product (Development Kits)

EVAL-ADUC7121QSPZ

功能描述:BOARD EVALUATION FOR ADUC7121 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:MicroConverter® ADuC7xxx 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF)

EVALADUC7121QSPZU1

制造商:Analog Devices 功能描述:QUICK START DEVELOPMENT SYSTEM - Boxed Product (Development Kits)

EVAL-ADUC7122QSPZ

功能描述:BOARD EVALUATION FOR ADUC7122 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:MicroConverter® ADuC7xxx 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF)